# Sample Analog Input and Key Input Routines Using a 4-channel Comparator

Application Note: KS57APN7

Application Engineering Department LSI 2 Division, Micom Sector

## **COMPARATOR APPLICATIONS**

#### OVERVIEW

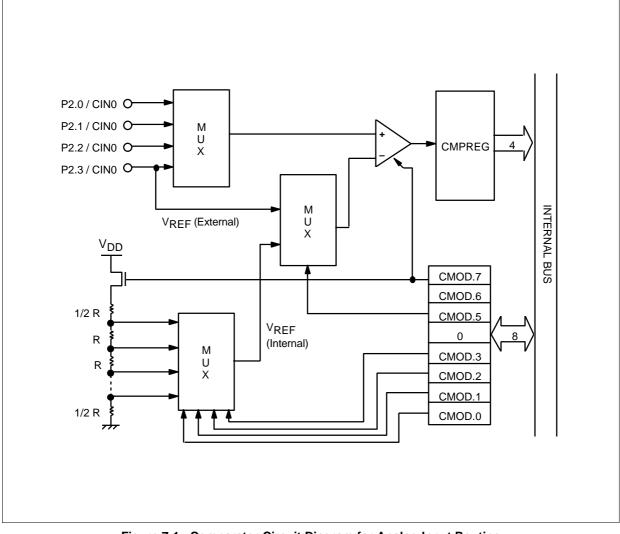

The KS57C0002 microcontroller has a 4-channel comparator. The reference voltage can be supplied either internally or externally at P2.3. The internal reference voltage is stepped in 16 levels. When a conversion is completed, the result is saved in the comparison result register, CMPREG.

CMOD register settings are used to control comparator operation. P2MOD register settings configure port 2 for analog or digital input. The comparator logic is as follows:

| lf "1": | Analog input voltago | $V_{p=2} + 150  mV_{p}$   |

|---------|----------------------|---------------------------|

| н.      | Analog input voltage | V <sub>REF</sub> + 150 mV |

If "0": Analog input voltage V REF - 150 mV

#### NOTE

Voltage (an analog quantity) that is applied to the port pins can be converted into digital data with 4-bit precision (see Figure 7-1).

#### ANALOG INPUT APPLICATION

#### **Function Description**

The program example presented in this section converts a voltage applied to any analog input port pin (CINn) into digital data. The program provides 4-bit resolution and changes the reference voltage in four steps.

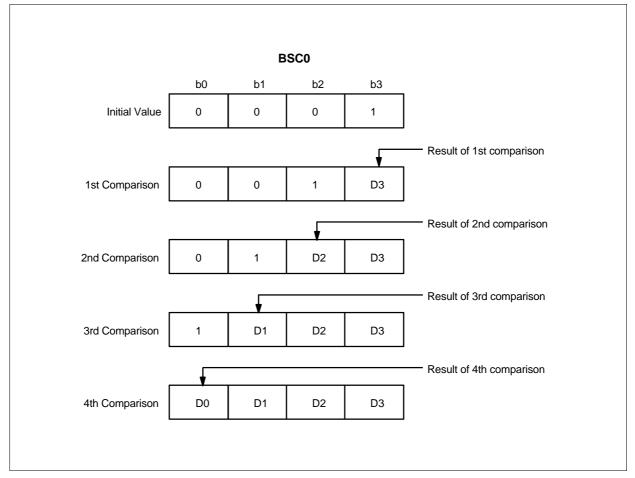

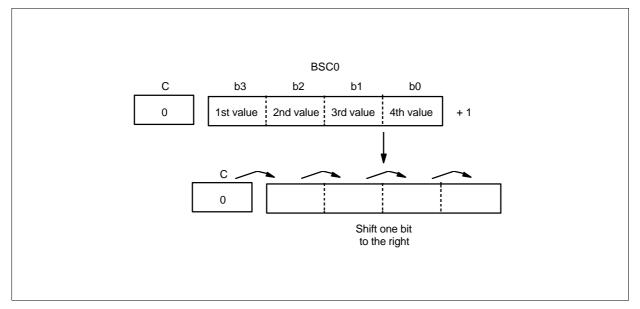

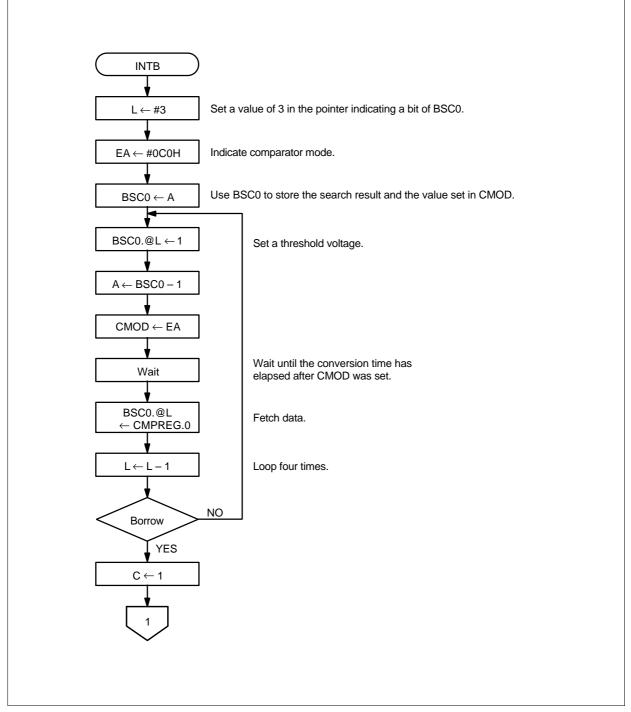

Each time the reference voltage is changed, it is compared with the voltage that is currently being applied to a given analog input port pin (CINn). The result of the comparison is then stored in bit sequential carrier 0 (BSC0), starting from the most significant bit. The threshold voltage is determined by the BSC0 value (see Figure 7-2).

More specifically, the program compares the values of the lower four bits of CMOD with the input pin voltage (CINn) in four steps, starting from a value of 0, and increasing to 0EH (reference voltage of 1/32  $V_{DD}$  to 29/32  $V_{DD}$ ). This operation is accomplished by means of a binary search.

The result of each comparison is stored in BSC0. By modifying the BSC0 value in CMOD, you can also compare the lower four bits of CMOD starting from 1 and increasing to 0FH (reference voltage of 3/32 V<sub>DD</sub> to 31/32 V<sub>DD</sub>).

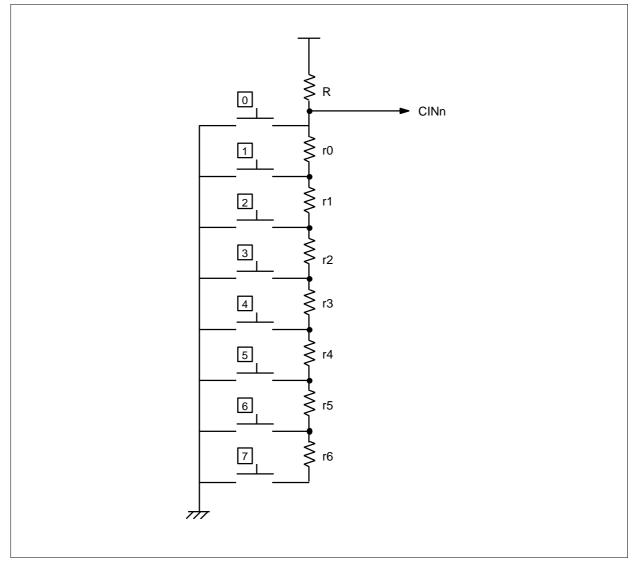

Figure 7-1. Comparator Circuit Diagram for Analog Input Routine

Figure 7-2. Storage of Comparison Results in BSC0

## **Programming Guidelines**

Hardware settings:

| $P2MOD \gets \#0H$                    | ; Set P2.0/CIN0 – P2.3/CIN3 to analog input                                        |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| High 4 bits of CMOD $\leftarrow$ #0CH | ; Internal reference: conversion time = 15.2 $\mu s$ @4.19 MHz; disable comparator |  |  |  |

| Nesting :                             | One level                                                                          |  |  |  |

| Hardware assignment:                  | Comparator input port 0 (CIN0)                                                     |  |  |  |

| Bit sequential carrier:               | BSC0                                                                               |  |  |  |

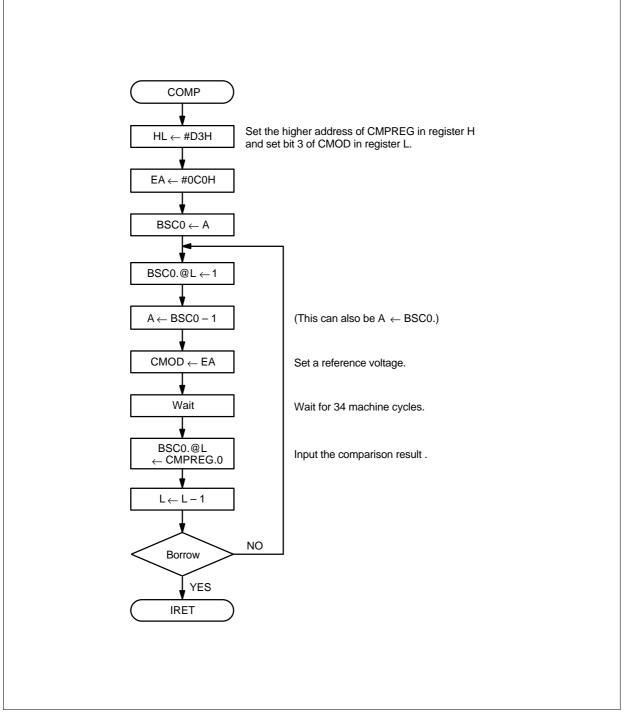

Figure 7-3. Program Flowchart for Analog Input Routine

## Source Code for Analog Input Routine

CHIP C:\SMDSII\DATA\57C0002.DEF

| ;====================================== |                                                                           |                                                                     |                                                                                                         |   |  |

|-----------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---|--|

| ; Comparator service routine:           |                                                                           |                                                                     |                                                                                                         |   |  |

| COMP                                    | BITS<br>SMB<br>LD<br>LD<br>LD                                             | EMB<br>15<br>HL,#0D3H<br>EA,#0C0H<br>BSC0,A                         | ; Set the highest 4 bits of CMPREG in register H ; Set bit 3 of CMOD in register L ; BSC $\leftarrow 0$ | 1 |  |

| LOOP                                    | BITS<br>LD<br>DECS<br>LD<br>LD                                            | BSC0.@L<br>A,BSC0<br>A<br>CMOD,EA<br>A,#0BH                         | ; Start comparison<br>; Wait 36 machine cycles                                                          |   |  |

| WAIT<br>; =======                       | DECS<br>JR<br>RCF<br>LD<br>AND<br>CPSE<br>CCF<br>LDB<br>DECS<br>JP<br>RET | A<br>WAIT<br>A,CMPREG<br>A,#0001B<br>A,#0<br>BSC0.@L,C<br>L<br>LOOP | ; Store the comparison result                                                                           |   |  |

#### **KEY INPUT ROUTINE**

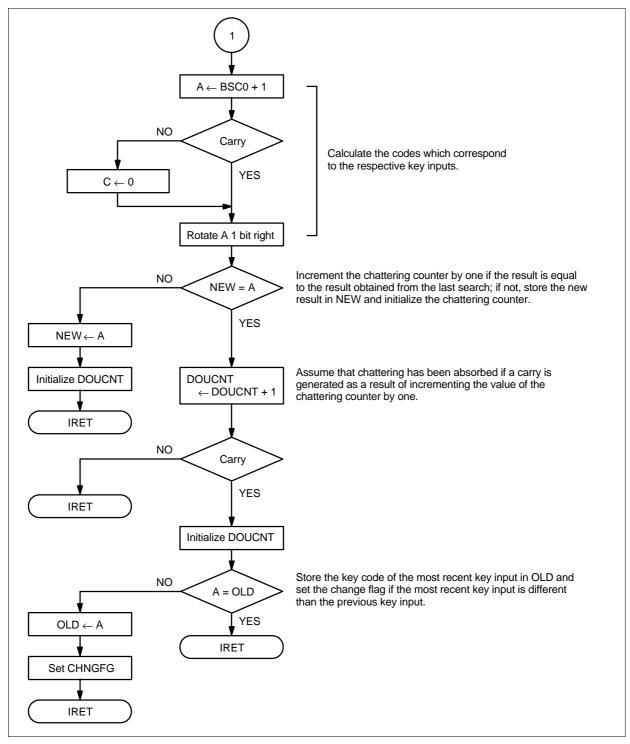

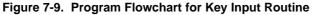

#### **Function Description**

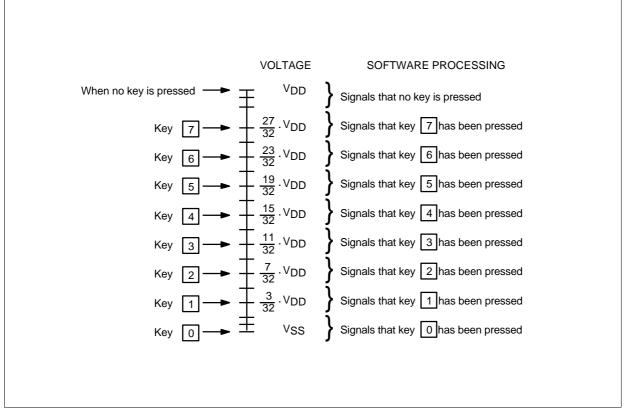

You can use comparator inputs CIN0–CIN3 to process key input signals. In the following sample program, the comparator is used to process input signals from up to 178 keys. When a key is pressed, a reference voltage is input to a comparator input pin. The input voltage is measured by software to determine which key has been pressed.

Figure 7-4 shows how the reference voltage is measured when one of the eight keys is pressed. The circuit diagram in Figure 7-5 shows how the reference voltage is applied to the specific input pin when one of the eight keys is pressed.

Figure 7-4. Eight-Key Example for Key Input Routine

Figure 7-5. Key Input Circuit

#### Determining the Resistance in a Key Input Circuit

To calculate the resistance of r0 to r6 (shown in Figure 7-5), use the following equation:

$$\sum_{k=0}^{n} rk = \frac{3+4n}{29-4n} R$$

To obtain the value of r0 to r6, substitute 0 to 6 for 'n' in the equation above. For example, if 'R' is 2.2 K $\Omega$ , then:

r0 = 240  $\Omega,$  r1 = 390  $\Omega,$  r2 = 510  $\Omega,$  r3 = 820  $\Omega,$  r4 = 1.3 k $\Omega,$  r5 = 2.4 k $\Omega,$  and r6 = 6.2 k $\Omega$

#### **Using the Binary Search Method**

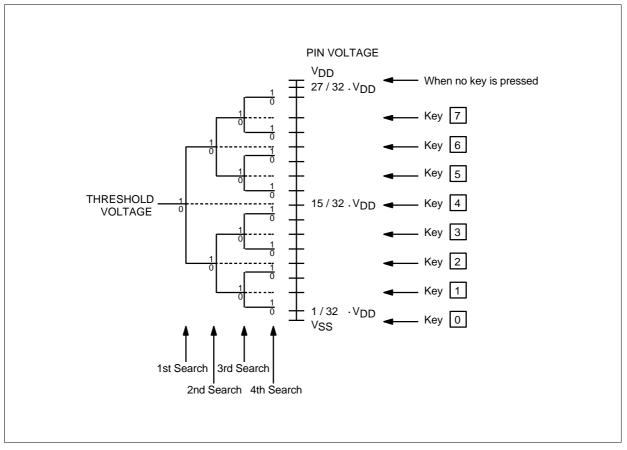

In the key input circuit, the key with the lower number takes precedence when two or more keys are pressed simultaneously. The sample program uses a binary search method to measure comparator input voltage. It performs four searches of the reference voltage, regardless of the pin voltage value. Figure 7-6 illustrates the binary search method and the corresponding key codes.

Figure 7-6. Binary Search Method for Key Input Routine

#### Procedure for Storing Key Code Reference Values

The vertical axis in Figure 7-6 indicates the value of the reference voltage applied to the pin when each of the keys shown on the right has been pressed.

The voltage value obtained during each search operation is stored in a register, starting from the highest bit toward the lowest. The value obtained during the first search is stored in bit 3 of the register, the value obtained during the second search is stored in bit 2, and so on. A decimal 1 is added to the voltage values stored in this manner. Then the contents of register are shifted right one bit to create codes that correspond to the respective keys. If no key is pressed, key code 8 is assumed.

For example, suppose key "3" is pressed. The value obtained by a binary search ("0101B" or "0110B") is stored in a register. In either case, add decimal 1 to the register value and shift the value one bit to the right. The result will be a 3 in decimal format, as illustrated below. Key code 3 is therefore assigned to key "3".

$$0101+1=0110B \xrightarrow{\text{shift}} 0011B$$

$0110+1=0110B \xrightarrow{\text{shift}} 0011B$

In the program example, key inputs are processed using the basic timer. It is assumed that the ON and OFF chattering times are 10 ms. Each time a key code changes, the change flag, CHNGFG, is set.

Figure 7-7. Key Code Store Operation

## **COMPARATOR APPLICATIONS**

### **RAM Allocation**

| Address                        | 50H       | 51H                                     | 52H    | 53H  |  |  |  |

|--------------------------------|-----------|-----------------------------------------|--------|------|--|--|--|

|                                | NEW       | OLD                                     | DOUCNT | FLAG |  |  |  |

|                                |           |                                         |        |      |  |  |  |

| NEW:                           | Store     | Stores the codes when chattering occurs |        |      |  |  |  |

| OLD:                           | Store     | Stores the key codes of valid keys      |        |      |  |  |  |

| DOUCNT:                        | Chat      | Chattering counter                      |        |      |  |  |  |

| CHNGFG (53H.0                  | 0): Char  | Change flag                             |        |      |  |  |  |

|                                |           |                                         |        |      |  |  |  |

| Programming Guidelines         |           |                                         |        |      |  |  |  |

| Hardware setting               | js:       |                                         |        |      |  |  |  |

| $BMOD \leftarrow \texttt{\#0}$ | FH ; Inte | ; Interval time = 1.95 ms               |        |      |  |  |  |

|                         | ,                               |

|-------------------------|---------------------------------|

| $P2MOD \gets \#0H$      | ; Set CIN0–CIN3 to analog input |

| Pin assignment:         | Comparator input pin (CIN0)     |

| Bit sequential carrier: | BSC0                            |

| Nesting:                | One level                       |

| Interrupt:              | INTB                            |

Figure 7-8. Program Flowchart for INTB Processing (Key Input Routine)

# Source Code for Key Input Routine

| Source Code for Key Input Routine      |                                                                             |                                                                                                              |                |                                                                                 |  |

|----------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------|--|

|                                        | CHIP                                                                        | C:\SMDSII\DATA\57C0002.DEF                                                                                   |                |                                                                                 |  |

| NEW<br>OLD<br>DOUCNT<br>CHNGFG         | EQU<br>EQU<br>EQU<br>EQU                                                    | 50H<br>51H<br>52H<br>53H.0                                                                                   | ·,<br>·,<br>·, | Key code when chattering<br>Valid key code<br>Debouncing counter<br>Change flag |  |

|                                        | ORG<br>VENT1                                                                | 0002H<br>0,0,INTB                                                                                            |                |                                                                                 |  |

| ; ==================================== |                                                                             |                                                                                                              | ==:            |                                                                                 |  |

| INITIAL                                | BITR<br>LD<br>LD<br>LD<br>LD<br>LD<br>LD<br>BITR<br>LD<br>BITS<br>EI<br>RET | EMB<br>A,#0<br>P2MOD,A<br>A,#0BH<br>DOUCNT,A<br>A,#8H<br>NEW,A<br>OLD,A<br>CHNGFG<br>A,#0FH<br>BMOD,A<br>IEB | ;              | Set CIN0–CIN3 to analog input                                                   |  |

| ; INTB processing:                     |                                                                             |                                                                                                              |                |                                                                                 |  |

| INTB                                   | PUSH<br>SRB<br>LD<br>LD<br>LD                                               | SB<br>1<br>L,#3H<br>EA,#0C0H<br>BSC0,A                                                                       | ;              | EMB = 0, ERB = 0; specify bit 3                                                 |  |

| LOOP                                   | BITS<br>LD<br>DECS<br>LD<br>LD                                              | BSC0.@L<br>A,BSC0<br>A<br>CMOD,EA<br>A,#0BH                                                                  | ;              | Start comparison                                                                |  |

# Source Code for Key Input Routine (Cont.)

| WAIT  | 5500                                    |                                                     |   |                                                  |

|-------|-----------------------------------------|-----------------------------------------------------|---|--------------------------------------------------|

|       | DECS<br>JR                              | A<br>WAIT                                           | ; | Wait for conversion time                         |

|       | RCF<br>LD<br>AND<br>CPSE<br>CCF         | A,CMPREG<br>A,#0001B<br>A,#0H                       |   |                                                  |

| LDB   | LDB<br>DECS                             | BSC0.@L,C<br>L<br>LOOP                              | ; | Store the conversion result                      |

|       | LD<br>CCF                               | A,BSC0                                              | ; | Calculate key code                               |

|       | ADS<br>RCF                              | A,#1                                                |   |                                                  |

|       | RRC                                     | А                                                   |   |                                                  |

|       | LD<br>CPSE<br>JP<br>INCS<br>POP<br>IRET | HL,#NEW<br>A,@HL<br>FKEY2<br>DOUCNT<br>SB           |   |                                                  |

|       | LD<br>LD<br>CPSE<br>JR<br>POP<br>IRET   | A,#0BH<br>DOUCNT,A<br>A,OLD<br>A,@HL<br>FKEY1<br>SB |   |                                                  |

| FKEY1 | LD<br>LD<br>BITS<br>POP<br>IRET         | A, @HL<br>OLD,A<br>CHNGFG<br>SB                     | ; | Set the conversion flag                          |

| FKEY2 | LD<br>LD<br>LD<br>POP<br>IRET<br>END    | NEW,A<br>A,#0BH<br>DOUCNT,A<br>SB                   | ; | Store key code in OLD<br>Set the conversion flag |

|       |                                         |                                                     |   |                                                  |